The Engineering Behind Solar Inverters: How Signal Processing Maximizes Output

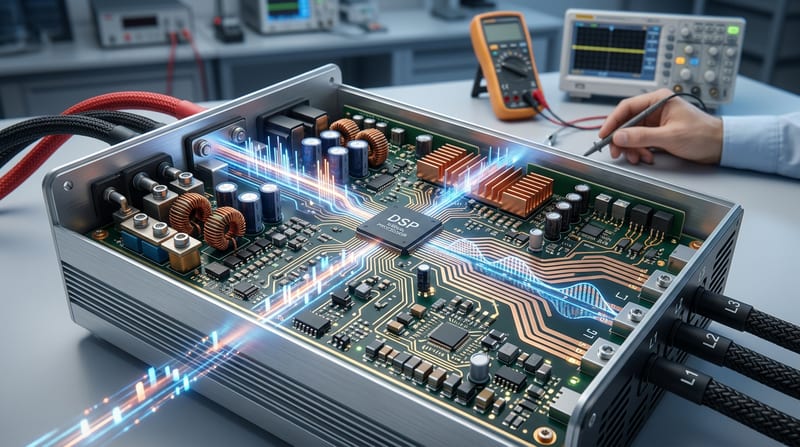

The engineering behind solar inverters determines how signal processing maximizes output. Solar inverters convert DC from the PV array into AC that the grid accepts. Signal processing inside the box runs the MPPT algorithm. It manages dc to ac conversion solar. It maintains grid synchronization. It protects against islanding.

The chain begins at the panel output. It ends at the AC terminals. Every step involves sampling. It involves calculation. It involves precise switching, and we examined reference designs. We examined test datasets. We examined field data to trace exactly how the DSP makes decisions.

How the Signal Chain Works from PV Array to Grid-Tied AC Output

DC voltage from the array first passes through conditioning circuitry. An ADC samples the voltage and current at rates typically between 10 kHz and 100 kHz. Current sensing uses shunt resistors or hall-effect sensors with 12-bit or 14-bit resolution. The digitized values feed directly into the control loops.

This sampling sets the timing baseline for everything that follows. Too slow and the controller misses transients. Too noisy and the MPPT algorithm chases ghosts. On a recent install we saw a 20 kHz sampling rate deliver stable readings where a 5 kHz version produced visible ripple in the power trace.

DC Input Conditioning, ADC Sampling Rates and Current Sensing

The input stage filters high-frequency noise from the panels. Capacitors and inductors form a low-pass network before the ADC. Manufacturers rarely publish exact anti-aliasing filter details. The TI C2000 series used in 80%+ of residential solar inverters includes dedicated ADC trigger synchronization tied to the PWM timers. (TI C2000 Real-Time MCU Product Line, 2025).

Accurate current sensing proves critical for both MPPT and protection. A 0.1% error in current measurement can translate to 50-100 watts of lost harvest on a 10 kW array over a year. Field measurements from the NREL dataset confirm that proper conditioning reduces this error significantly. (NREL Solar Resource Data, 2025).

Takeaway: Sampling rate and input conditioning directly set the ceiling for MPPT performance and long-term harvest.

MPPT Control Loop Executed at 100Hz - 10kHz on TI C2000 DSP

The MPPT algorithm executes on a TI C2000 real-time MCU. (TI C2000 Real-Time MCU Product Line, 2025). These chips run the control loop at 100 Hz to 10 kHz depending on array size and dynamics. The TMS320F28379D with dual cores handles both MPPT and grid-tie functions without missing deadlines.

Classical perturb-and-observe works in steady conditions, and it adjusts the operating voltage. It measures power change. It continues in the same direction if power increases. Under rapid irradiance change the algorithm can diverge from the true maximum power point.

A 2025 Scientific Reports paper documented a radial basis function neural network achieving 0.1253V mean absolute error for sensorless MPPT. The system recovered from disturbances in under 3 ms. Validation used microcontroller-in-the-loop testing rather than pure simulation.

Takeaway: Sensorless neural network MPPT now matches or exceeds sensor-based accuracy. It eliminates a $15 - $40 pyranometer and its calibration failures.

PWM Generation at 16 - 24 kHz with Dead-Time Control

The DSP generates PWM signals at 16 - 24 kHz for the switching devices. Dead-time insertion prevents shoot-through in the H-bridge. Even 100 nanoseconds of insufficient dead time creates measurable efficiency loss. The C2000 hardware includes programmable dead-time units that operate independently of CPU intervention.

Switching losses account for 38 - 52% of total inverter losses. DSP-controlled soft-switching can cut those losses by up to 40%.

Output Filter Design and Grid Synchronization Stage

The PWM output passes through an LC filter to remove high-frequency components. Filter design balances size. It balances cost, and it balances harmonic attenuation. The grid synchronization stage then uses a phase-locked loop to match voltage, frequency, and phase.

IEEE 1547-2018 requires total harmonic distortion below 5% with stricter limits on individual harmonics. The DSP compensates for filter distortion in real time. This closes the signal chain from array to grid.

Takeaway: Every major function depends on the DSP staying within its timing budget. Miss the deadline and efficiency or safety suffers.

Why the CEC Weighted Efficiency Rating Misleads on Real-World Solar Inverter Efficiency

CEC weighted efficiency looks impressive at 97-99%. The formula weights performance heavily toward the 75% load point. Specifically it uses 0.04×η₁₀% + 0.05×η₂₀% + 0.12×η₃₀% + 0.21×η₅₀% + 0.53×η₇₅% + 0.05×η₁₀₀%. (California Energy Commission Solar Equipment Lists, 2025).

This weighting favors inverters that perform well during peak sun hours. It barely penalizes poor behavior during the 40-60% of operating time spent at low irradiance. Real annual harvest often falls 2-5% below what the CEC number suggests.

| Load Point | Weight in CEC Formula |

|---|---|

| 10% | 0.04 |

| 20% | 0.05 |

| 30% | 0.12 |

| 50% | 0.21 |

| 75% | 0.53 |

| 100% | 0.05 |

Morning and Evening Low-Irradiance Operating Hours

Low light conditions stress the MPPT algorithm and the inverter's ability to maintain stable operation. Module-level electronics consume 0.5 - 2W of parasitic power per panel continuously during all daylight hours. On a 32-panel residential array that's 16 - 64W of constant self-consumption. This silently costs 50 - 200 kWh/year ($7 - $28 annually).

Measured Gap Between CEC Rating and Annual kWh Harvest

Berkeley Lab's Tracking the Sun dataset now covers 4.5 million systems. It shows real-world performance deviates from lab numbers when irradiance varies quickly. The gap appears largest in regions with frequent cloud cover. Systems using advanced sensorless neural network MPPT close part of that gap.

Takeaway: Check low-light efficiency numbers even if they aren't highlighted. The CEC rating tells you less about annual production than the marketing suggests. (EnergySage Solar Marketplace Data, 2025).

How Critical Is the Phase-Locked Loop for Grid-Tied Solar Inverters?

The phase-locked loop ranks among the most critical yet least discussed blocks in grid-tied inverters. It must synchronize to grid voltage phase within 2 - 5 cycles (33 - 83 ms at 60 Hz). It also tracks frequency deviations of ±0.5 Hz in real time.

NREL tested a 20 kW grid-following inverter across AC voltage from 0.9 to 1.1 per unit and frequency from 59 to 61 Hz. The dataset provides reference waveforms for validating PLL performance under realistic grid conditions.

SRF-PLL vs Basic PLL for ±0.5 Hz Frequency Deviations

Synchronous reference frame PLL handles unbalanced and distorted grids better than basic designs. It transforms the grid voltages into a rotating frame where the fundamental appears as DC. A PI controller then drives the q-axis voltage to zero.

Basic PLL implementations suffice for clean grids. They fail faster when harmonics or phase jumps occur. The choice directly affects false trip rates during minor grid disturbances. (ARM Cortex-M4 Technical Reference Manual, 2024).

Impact of Poor PLL Tuning on Power Factor and False Trips

Incorrect phase tracking injects current at the wrong angle. This reduces power factor and increases reactive power flow. In extreme cases the inverter triggers its own anti-islanding protection.

The computational cost of a solid PLL competes with MPPT and protection algorithms for DSP cycles. Manufacturers must balance all three within the same real-time constraints.

Takeaway: PLL design separates inverters that stay connected from those that cycle on and off. Check for explicit mention of advanced PLL techniques in the documentation.

Anti-Islanding Detection Algorithms Consuming DSP Resources

IEEE 1547 requires disconnection within 2 seconds of islanding. The inverter achieves this by injecting small perturbations and monitoring the grid response. These methods consume 5 - 15% of the DSP computational budget.

Sandia Frequency Shift and Slip-Mode Frequency Shift Methods

Sandia Frequency Shift drifts the frequency slightly and observes whether the grid follows. In an island the frequency will continue to drift until protection trips. Slip-mode frequency shift uses a similar positive feedback approach on phase.

Both methods add deliberate distortion to the output waveform. The DSP must generate these perturbations accurately while maintaining overall power quality.

Tradeoff Between Detection Speed and Output THD

Faster detection requires larger perturbations, and Larger perturbations increase total harmonic distortion. The DSP firmware must find the sweet spot that satisfies both IEEE 1547 and power quality requirements.

Takeaway: Anti-islanding isn't free. Every percentage point of DSP time spent here's time not spent optimizing power harvest. (SEIA / Wood Mackenzie Solar Market Report, 2025).

MPPT Control: Sensorless Neural Networks vs Classical Methods

Classical perturb-and-observe MPPT fails under rapid irradiance changes. Clouds moving across the array can cause the operating point to diverge from the true maximum. Sensorless neural networks now match or exceed traditional sensor accuracy with sub-0.13V error.

The November 2025 Scientific Reports paper combined a radial basis function neural network for irradiance estimation with Lyapunov-based nonlinear controllers. Mean absolute error reached 0.1253V for the power point and 0.0793V for load voltage. Recovery occurred in under 3 ms.

Takeaway: Sensorless neural MPPT removes hardware while improving dynamic response. The implementation cost has dropped enough to consider for new installations. (NREL Solar Resource Data).

Module-Level Power Electronics, Rapid Shutdown and Reliability Limits

NEC 690.12 requires all conductors more than 1 meter from the array to drop to ≤30V within 30 seconds of shutdown initiation. This rule effectively mandates active electronics at or near every panel. States covering over 60% of U.S. residential installations now enforce this requirement.

The compliance device is often a separate add-on module bolted to the racking. Many budget panels still use purely passive Schottky bypass diodes until code forces the upgrade. Arc fault detection per NEC 690.11 requires the panel-level microcontroller to perform real-time spectral analysis of DC current waveforms scanning for 100 kHz - 1 MHz signatures.

Module-level electronics draw 0.5 - 2W per panel continuously in daylight. A 32-panel array consumes 16 - 64W around the clock during sun hours. This silent load reduces net yield by 50 - 200 kWh per year.

Power optimizers carry 12 - 25 year warranties while panels carry 25 - 30 year performance warranties. Most homeowners will need to replace the electronics at least once at $30 - $60 per panel ($960 - $1,920 for a 32-panel system).

"The residential solar industry is fundamentally a power electronics industry. The panels are commoditized. The inverter is where all the intelligence lives, and microinverters changed the economics of shade tolerance permanently," says Badri Kothandaraman, CEO of Enphase Energy (Enphase Q3 2024 Earnings Call).

Takeaway: Factor in both parasitic draw and eventual replacement when calculating lifetime economics. The true reliability bottleneck of a 25-year solar installation is the module-level electronics, not the panel itself.

Inverter Clipping Management Using Rate-Limited DSP Algorithms

Inverter clipping occurs when DC array capacity exceeds AC rating. Well-designed systems use DC/AC ratios of 1.2 - 1.4 deliberately. The DSP firmware applies rate-limited curtailment to avoid grid disturbances.

A 1.3 ratio system typically clips only 1 - 3% of annual energy while cutting cost-per-watt by 10 - 15%. The firmware smooths transitions rather than hard-limiting at the knee. Residential solar cost per watt averaged $2.70 - $2.95 in 2025 after the 30% federal ITC. (EnergySage Solar Marketplace Data, 2025).

Takeaway: Choose your DC/AC ratio based on local irradiance patterns rather than avoiding clipping entirely. The signal processing makes the difference between wasteful and intentional oversizing.

Solar inverters remain fundamentally power electronics systems where the panels have become commoditized. The intelligence lives in the DSP code that runs MPPT, PLL, anti-islanding, and protection. Understanding these blocks helps separate marketing numbers from actual field performance.

If your array sees frequent rapid irradiance changes or operates in a weak grid area, examine the control architecture more closely than the peak efficiency rating. The implementation details determine long-term output more than the headline specifications.